4.1. 部署 SoC 至 FPGA

综合好的 YADAN SoC 的 .bit 文件为 Yadan.bit,PULPino SoC 的为 pulpino_zeroriscy.bit,分别可在下边两个链接中找到。

-

YADAN SoC: https://gitee.com/verimake/yadansoc/tree/master/prj

-

PULPino SoC: https://pan.baidu.com/s/1uzZ-Ic4XPclwRXgk5f-Z_g (提取码: 3005, 在 “Zeroriscy内核开发工具” 文件夹中)

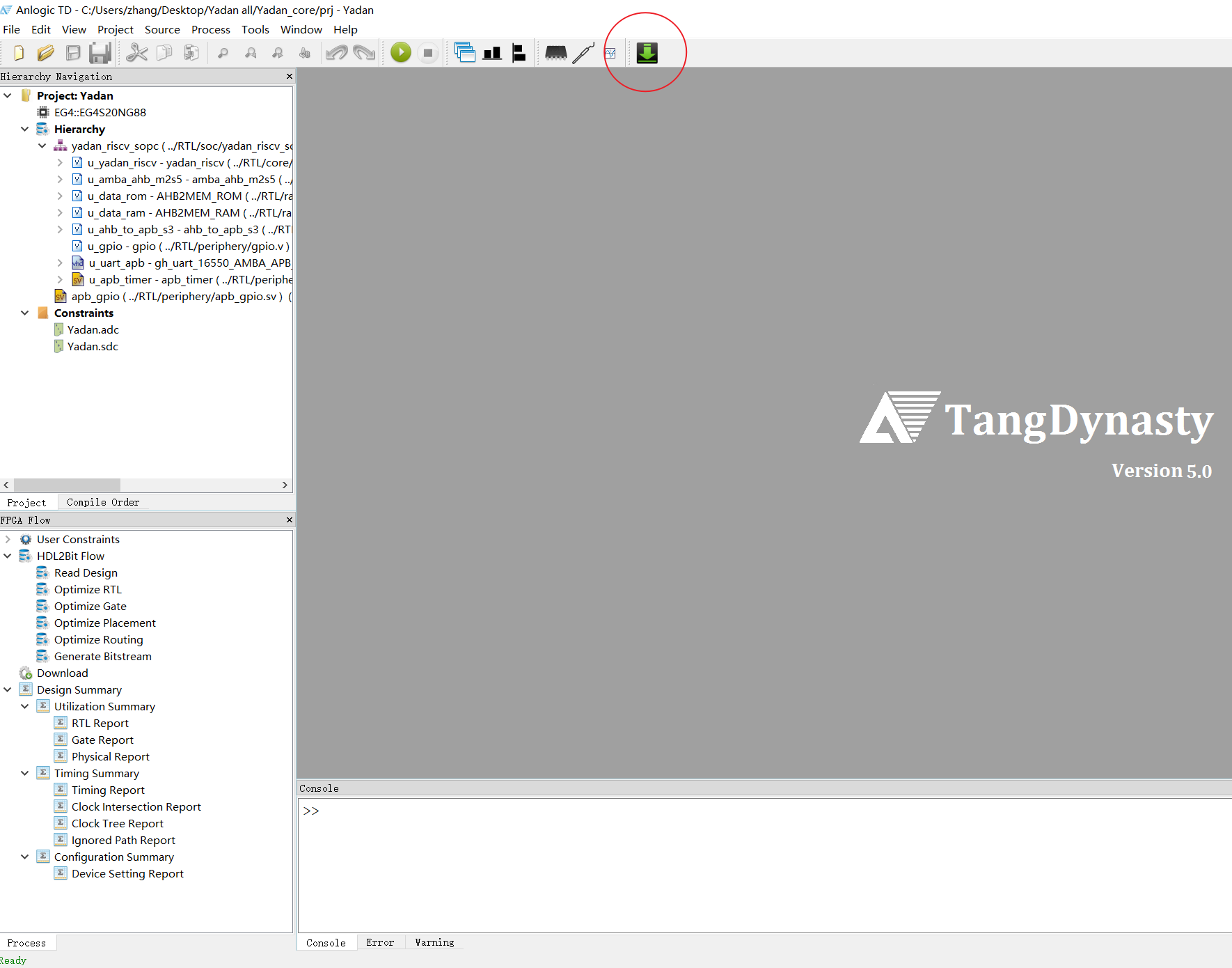

打开安装好的 TD 软件,点击如图 4.1 所示的按钮打开下载工具。

图 4.1 TD 软件中打开下载工具的按钮

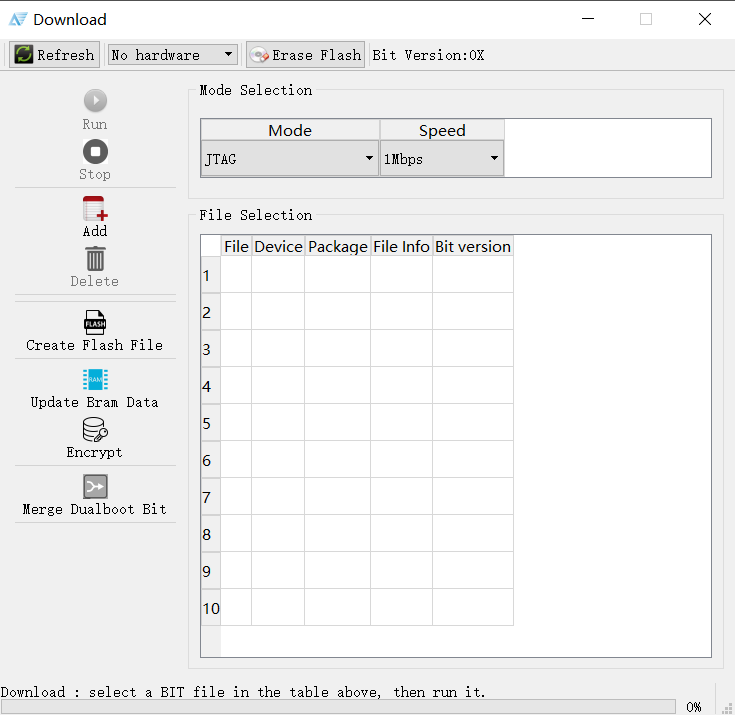

打开的下载工具的界面如图 4.2。

图 4.2 下载工具的界面

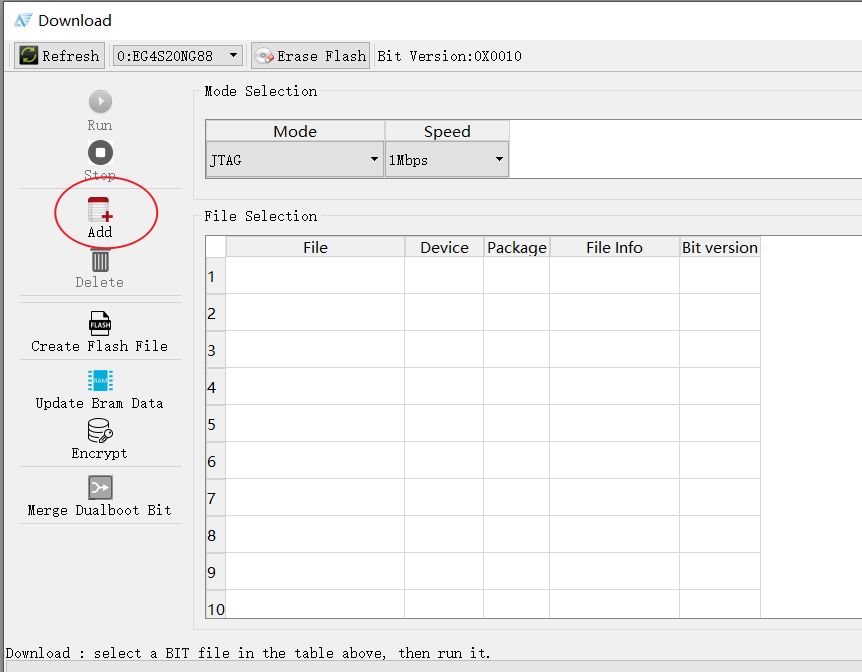

将 YADAN Board 通过 Type-C USB 线与 PC 机相连,下载工具中原先显示 No hardware 的下拉框就会自动更新为 EG4S20NG88(如果加载不了需要检查下载器驱动是否正确安装,详情见第 3.3 节)。加载成功开发板后,界面如图 4.3 所示。

图 4.3 下载工具加载成功开发板后的界面

然后点击如图 4 所示的 Add 按钮,添加你想部署的 SoC 的 .bit 文件。

图 4.4 下载工具中的 Add 按钮

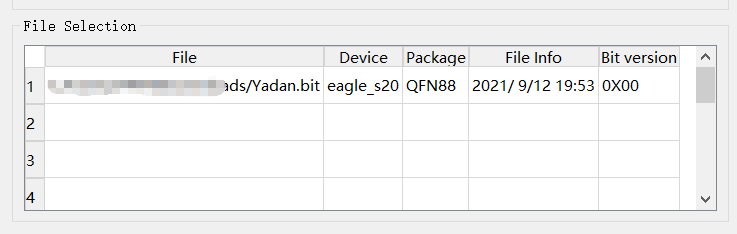

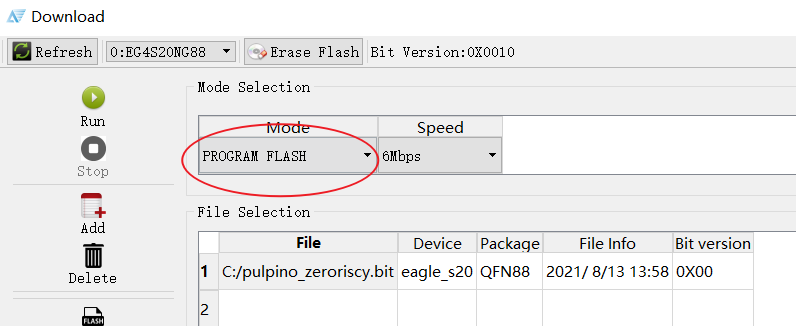

添加 .bit 文件完成后,可以看到文件的相关信息,包含该文件适用的芯片型号、封装、生成时间等,如图 4.5 为例。

图 4.5 显示的 Yadan.bit 的文件信息(如果用 PULPino,也能看到类似的内容)

Mode Selection 中可以选择下载模式,默认的下载模式为 JTAG 模式,适用于调试,但配置会在掉电后丢失。如果我们希望下次上电后 FPGA 能自动加载配置,则需要把配置下载到 FPGA 的配置芯片外置的 Flash 中,即我们需要选择下载模式为 PROGRAM FLASH 模式。下载速度默认为 1Mbps,我们可根据电脑和线材条件自由选择,但如果下载失败,需尝试降低下载速度再重新下载。选择下载模式的下拉框如图 4.6 所示。

图 4.6 选择下载模式的下拉框

在该模式下载完成后,开发板每次上电时,会先将 Flash 中存储的配置数据自动加载到 FPGA 中。

评论:

ESP32 外部中断

外部中断是单片机实时地处理外部事件的一种内部机制。

Micro:bit V2与M5GO V2全面对比

本文从硬件、软件、生态、价格、延展性方面对Micro:bit V2和M5GO v2进行全面的对比,供大家选型参考。

Python Turtle库从入门到精通

本教程讲解如何使用Python turtle库进行编程,并介绍了一些非常重要的编程概念。您将知道如何处理变量初始化、循环、条件语句、缩进、列表和操作符。

App Inventor 编程实例及指南-第12章 遥控机器人

本章将创建一个应用,将Android手机变成LEGO MINDSTORMS NXT 机器人的遥控器。

46亿年的奇迹 : 地球简史

一套拥有13本书,50个专题,1000+科学条目和知识点,近3000张绝美配图的科普读物。

3D打印兼容可定制LEGO基础块

3D打印兼容可定制LEGO基础块,套件缺件不要急,3D打印高精兼容块,想要什么颜色就打什么颜色。

两大青少年编程等级考试标准全解读,看这一篇就够了!

随着国家持续推进AI与科学教育的发展,以及大量资本的入场,少儿编程教育市场呈火热趋势,目前市场上已有超过200家少儿编程公司,并且这一趋势很可能依旧延续。虽然对于孩子是否必须学编程,行业内仍存在着不同的声音,但不可否认,少儿编程正在由“非刚需”向“刚需”逐渐转变。

在ESP32上实现WEB交互界面

本文主要介绍在未联网(AP热点)情况下实现WEB交互界面的CSS和javascript库。

Wio Terminal

Wio Terminal 微型计算机是由 Seeed 自主研发,内置多种物联网设备,拥有丰富的接口且同时支持无线数据连接,适合处理各种物联网项目。

YADAN Board 开发板

作者:VeriMake 共11讲YADAN Board 是一块核心为 Anlogic FPGA 的可编程硬件设计学习平台,我们既能直接写硬件描述语言 (HDL) 在里边实现特定的数字系统、甚至是 CPU 与 SoC,又能部署 SoC 后将其视为常规 SoC 来写软件开发。