1. 第一个实机实验

0. 引言

YADAN Board 的主芯片是一颗来自安路科技的 FPGA,所以我们也可以用 YADAN 来学习数字电路与硬件描述语言 (Hardware Description Language, HDL)。

本文将使用 Verilog,介绍如何使用安路科技提供的 TangDynasty 开发工具 (以下简称 TD 工具),从零开始在 YADAN Board 上做个按按键控制 LED 的项目。如果你想学习 VHDL、SystemVerilog 或其他 HDL,部分操作步骤也可以参考本文,因为 TD 工具可能也支持。

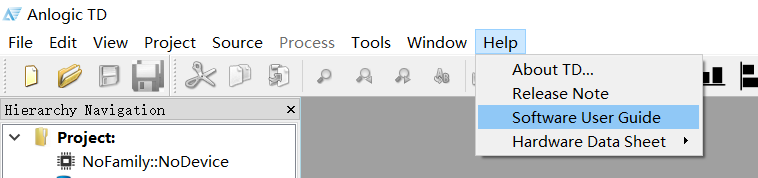

想了解更详细的 TD 工具的使用方法,也可以在 TD 软件中点击如图所示这个按钮阅读软件手册。

1. 实验内容

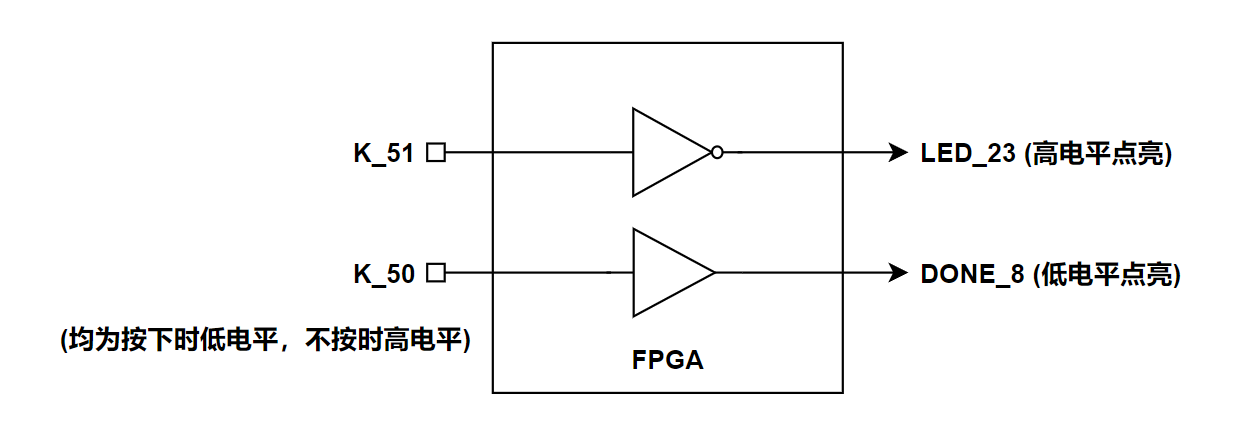

观察 YADAN Board,可以发现上边有 K_51 和 K_50 两个按键,右侧还有 LED_23 和 DONE_8 两个 LED,所以我们可以设计一个非常简单的实验,即使用两个按键分别控制两个 LED 的亮灭。通过这个简单的实验,我们可以了解如何使用 TD 工具来给 FPGA 编程。

阅读 YADAN 文档中对板载按键和 LED 的介绍,可以发现:

- 两个按键均为被按下时输出低电平,不被按时输出高电平

- LED_23 会在接收高电平时点亮,而 DONE_8 会在接收低电平时点亮

所以,我们可以在 FPGA 内构建如下图所示的数字逻辑,实现按住 K_51 时点亮 LED_23,按住 K_50 时点亮 DONE_8。

2. 创建项目

如果你还没安装 TD 工具,请先参考 YADAN 文档的第 3.2 节 去安装。

在使用 TD 工具新建项目之前,我们可以先参考下边这样的目录层次,在 <你想放的地方> 来自己先创建几个文件夹,这样在后期文件较多的时候会更方便整理:

* 注 1:建议路径与项目名只包含 ASCII 字符集内的英文、数字与部分简单符号,不要包含中文与特殊符号

* 注 2:目录层次与个人习惯有关,此处仅为一种方案,也可根据自己习惯来调整

<你想放的地方>/blink (项目名,此处以 blink 为例)

|

├─prj_td

| └─<与开发工具和平台相关的文件>

|

├─src

| └─<代码源文件>

|

└─<测试代码、文档、说明等其他文件>

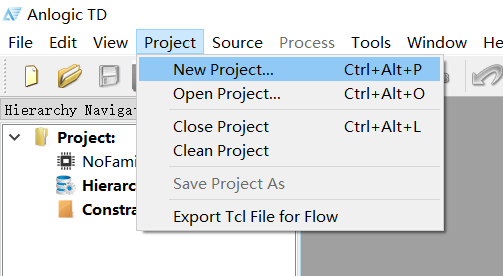

打开 TD 工具,点击 Project - New Project... 即可打开新建项目向导。

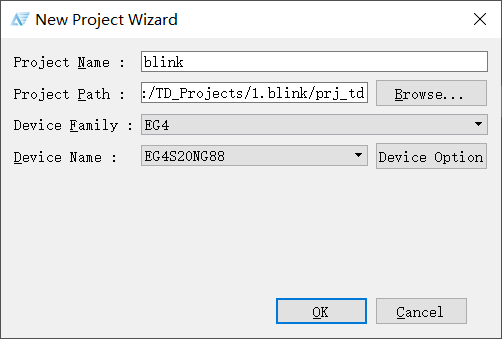

可根据界面中的提示,填写项目名、设置项目文件 .al 文件的存储路径、选择器件型号。比如我们可以将项目取名为 blink,把 .al 项目文件存储在 <你想放的地方>/blink/prj_td 目录,并选择 YADAN Board 上的 FPGA 的型号 EG4S20NG88。

点击 OK 即创建完成,可以发现 blink/prj_td 目录下新增了一个 blink.al 文件,该文件就是项目文件,以后我们可以直接双击它来打开这个项目。

3. 添加源文件

我们可以在 TD 工具中点击 File - New 来创建新文件,也可以直接在外边创建,不过要注意的是,Verilog 代码文件的后缀为 .v,比如可以创建 blink_top.v 文件。

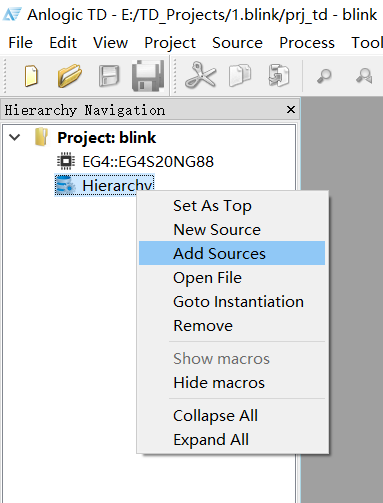

创建好源文件之后,右击 Hierarchy Navigation 中的 Hierarchy,再在弹出的菜单内点击 Add Sources 可以向项目中添加源文件。

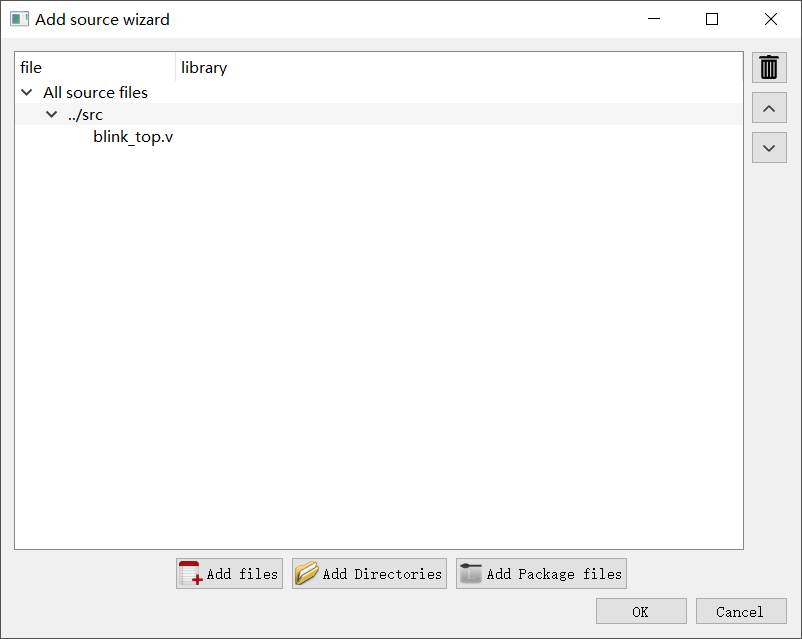

可以添加单个文件,也可以像下图一样直接把 blink/src 文件夹添加进项目。

添加完成后,Hierarchy 里边暂时不会显示没有有效代码的 .v 文件,我们打开 blink_top.v,根据先前在“实验内容”一节展示的数字逻辑,填入对应的 Verilog 代码:

module blink_top(input BUTTON_A,

input BUTTON_B,

output LED_A,

output LED_B);

assign LED_A = ~BUTTON_A;

assign LED_B = BUTTON_B;

endmodule

保存,即准备好了源代码,也能在 Hierarchy 里边看到这个文件了。如果该文件没有被识别为顶层模块,你也可以右键它然后点击 Set As Top 将其设置为顶层模块,顶层模块的概念类似编程语言中的 main() 函数。

4. 设置约束

上边的 Verilog 代码虽然描述好了数字逻辑,但 BUTTON_A 等各个端口还只是个名字,没有与 YADAN Board 实物上的引脚产生联系,所以我们需要设置约束。对于 TD 工具,约束分为 IO 约束与 SDC 约束,可分别由 .adc 与 .sdc 文件来设置。本实验不包含时序逻辑电路,所以只需设置 IO 约束,而不必设置 SDC 约束。

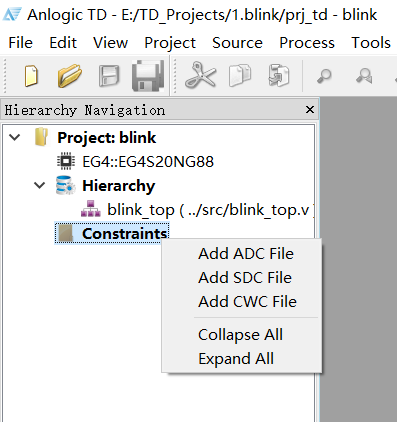

我们可以自己参考 TD 工具的软件手册中的说明,直接编写这些约束文件,然后右击 Hierarchy Navigation 中的 Constraints 来添加。

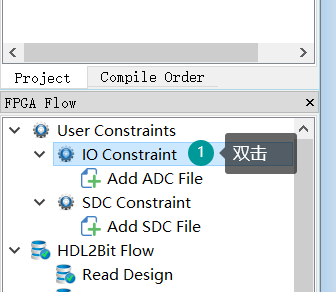

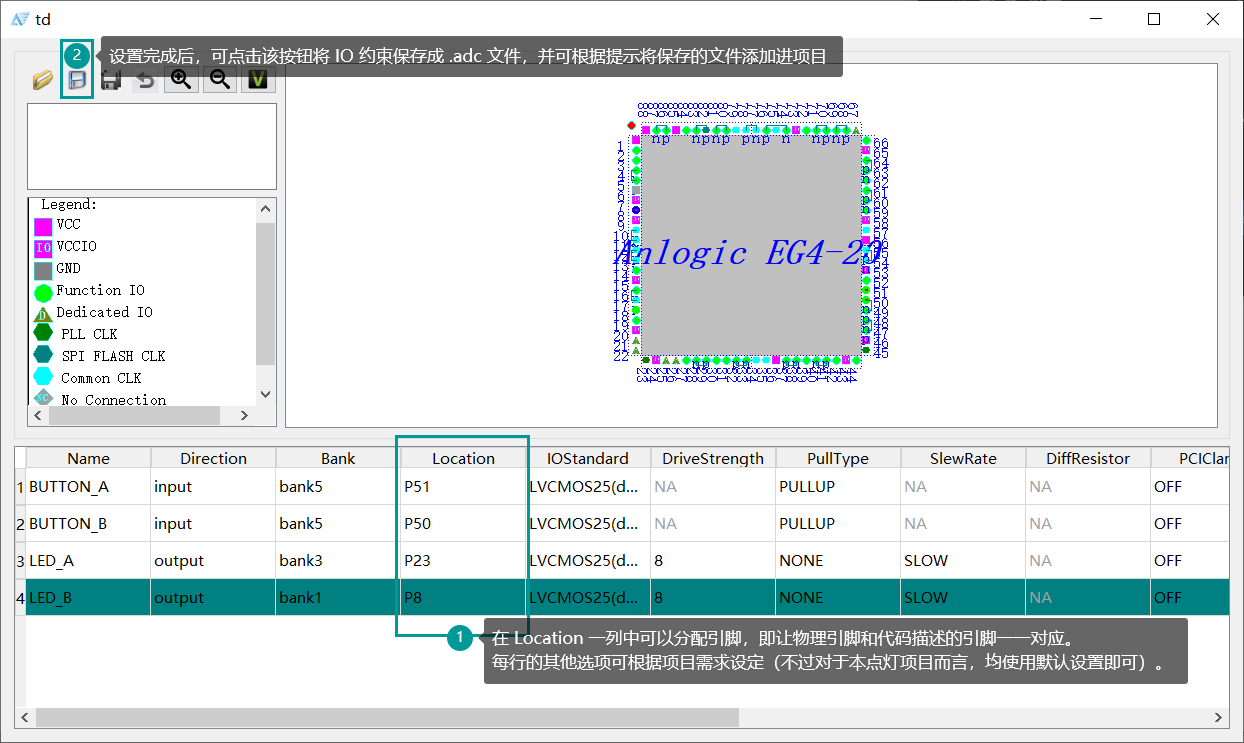

不过,TD 工具提供了更简单的方式来设置约束,双击 FPGA Flow 中的 IO Constraint,即可打开图形化的 IO 约束设置界面。

我们阅读 YADAN 文档中对 Board 的介绍,可以知道各个按键与 LED 分别连接了 FPGA 的哪些引脚。

然后在刚才打开的 IO 约束设置界面中,根据下图指引,为代码描述的端口分配一一对应的物理引脚。

设置完成后,项目文件夹内至少存在这些文件:

<你想放的地方>/blink

|

├─prj_td

| ├─blink.al

| └─blink.adc

|

└─src

└─blink_top.v

5. HDL2Bit

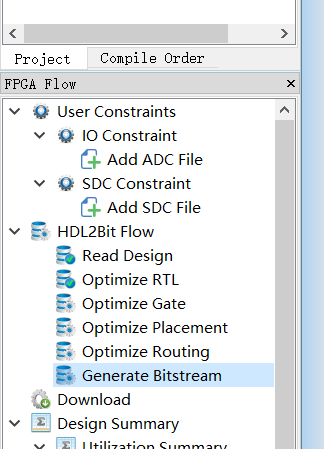

写好代码设置好约束后,可以在 FPGA Flow 中做些优化和检查,也可以双击 Generate Bitstream 生成可烧录给 FPGA 的 .bit 比特流文件。

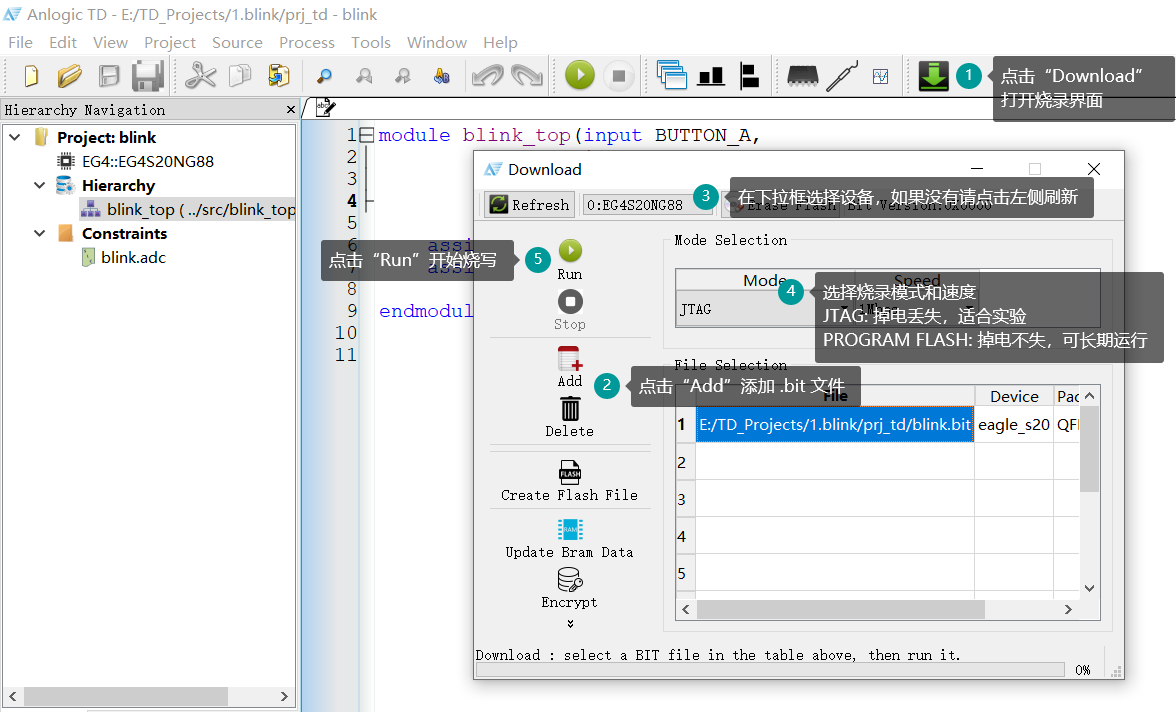

等待一段时间生成完成后,在 blink/prj_td 目录下可找到 blink.bit 文件,可在 TD 工具中打开烧录界面将其烧录给 FPGA,步骤如下图所示:

烧录完成后,按按开发板上的按键,就能见到如下边动图所示的现象了,FPGA 真神奇!

到了这里,你就成功在实机上跑好一次 Verilog 实验了。

可选:配置 VS Code 对 Verilog 的支持

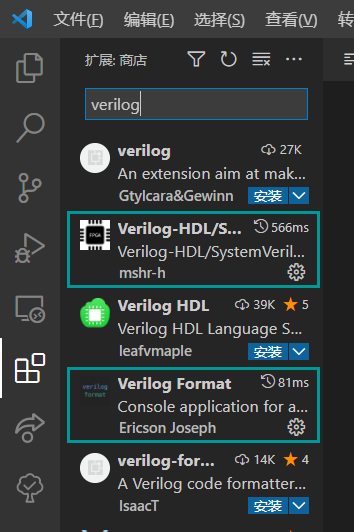

VS Code 是个非常强大的编辑器,当然也能用来编辑 Verilog 代码,只需安装下图中框出的两个扩展即可。第一个扩展可提供语法高亮等基础支持,第二个扩展可以格式化 Verilog 代码。

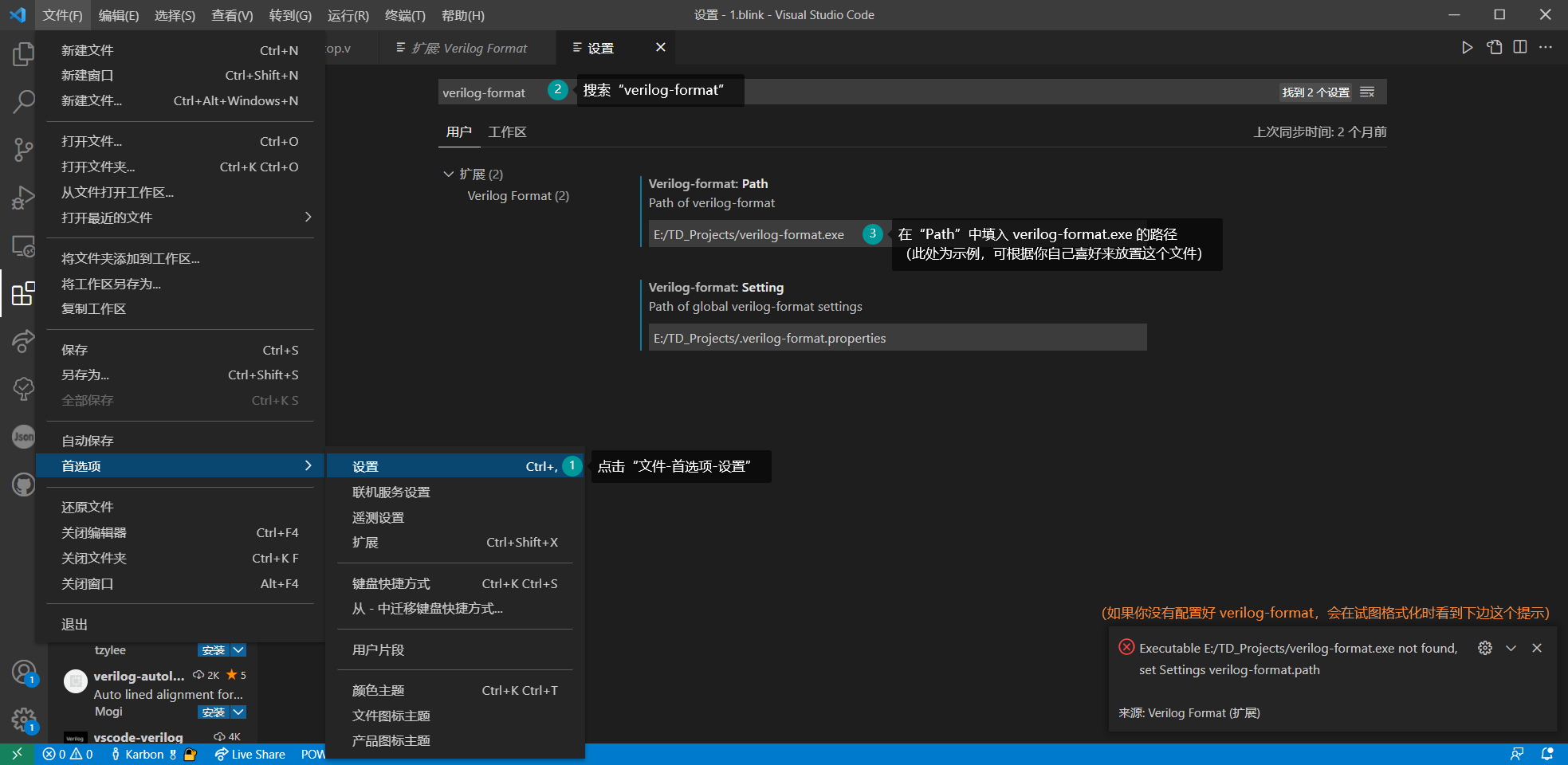

要注意的是,Verilog Format 扩展还需要配置好 verilog-format 的路径才能运行,请下载它,然后再根据下图所示的步骤,在 VS Code 的设置里边的 verilog-format.path 一项中填入它的路径。

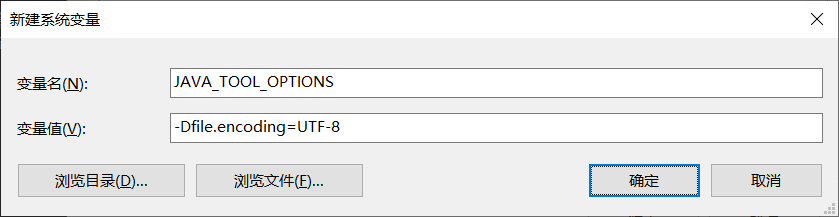

如果你需要格式化的代码包含中文,还需要将 JAVA 环境的默认编码设为 UTF-8,这样 verilog-format 才能正确处理以 UTF-8 编码的代码文件里边的中文等 ASCII 字符集之外的文字与符号。只需打开环境变量设置,添加名为 JAVA_TOOL_OPTIONS、值为 -Dfile.encoding=UTF-8 的系统变量即可。

评论:

在 YADAN Board 上入门 Verilog

作者:VeriMake 共5讲本系列材料共有 5 个主线章节 与 若干个额外示例,主线章节可帮助你基本了解 Verilog 与 TangDynasty 开发工具的使用方法,额外示例可在你需要开发更丰富的应用时提供参考。