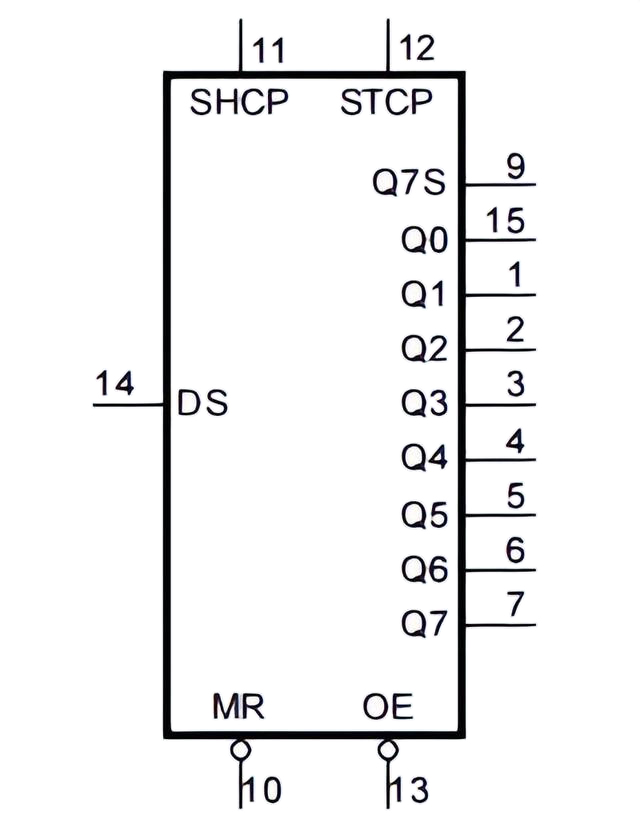

74HC595

74HC595是一个8位串行输入、并行输出的位移缓存器。并行输出为三态输出。

74HC595是一个8位串行输入、并行输出的位移缓存器。并行输出为三态输出。在SCK 的上升沿,串行数据由SDL输入到内部的8位位移缓存器,并由Q7' 输出,而并行输出则是在LCK的上升沿将在8位位移缓存器的数据存入到8位并行输出缓存器。当串行数据输入端OE的控制信号为低使能时,并行输出端的输出值等于并行输出缓存器所存储的值。

|

符号

|

引脚

|

描述

|

|

Q0--Q7

|

第15脚,第1-7脚

|

8位并行数据输出

|

|

GND

|

第8脚

|

地

|

|

Q7’

|

第9脚

|

串行数据输出

|

|

/MR

|

第10脚

|

主复位(低电平有效)

|

|

SH_CP

|

第11脚

|

数据输入时钟线

|

|

ST_CP

|

第12脚

|

输出存储器锁存时钟线

|

|

/OE

|

第13脚

|

输出有效(低电平有效)

|

|

DS

|

第14脚

|

串行数据输入

|

|

VCC

|

第16脚

|

电源

|

|

输入

|

输出

|

功能

|

|||||

|

SHCP

|

STCP

|

OE

|

MR

|

DS

|

Q7’

|

Qn

|

|

|

×

|

×

|

L

|

L

|

×

|

L

|

NC

|

MR为低电平时仅仅影响移位寄存器

|

|

×

|

↑

|

L

|

L

|

×

|

L

|

L

|

清空移位寄存器到输出寄存器

|

|

×

|

×

|

H

|

L

|

×

|

L

|

Z

|

清空移位寄存器,并行输出为高阻状态

|

|

↑

|

×

|

L

|

H

|

H

|

Q6’

|

NC

|

逻辑高电平移入移位寄存器状态0,包含所有的移位寄存器状态 移入

|

|

×

|

↑

|

L

|

H

|

×

|

NC

|

Qn’

|

移位寄存器的内容到达保持寄存器并从并口输出

|

|

↑

|

↑

|

L

|

H

|

×

|

Q6’

|

Qn’

|

移位寄存器内容移入,先前的移位寄存器的内容到达保持寄存器并出

|

本题是通过在串口监视器输入框中,输入相应的内容,控制一位数码管相应字段的点亮和熄灭。

本题要求通过数码管动态显示由串口输入数字的笔划。

本题是通过点击按键控制数码管显示数据在1~5~1之间循环变化。